- Главная

- Информатика

- Аппаратурная реализация кодера

Содержание

- 2. ния Рис. 4. Логический элемент сложения по модулю 2; а — функциональная схема; б - условное

- 3. Рис. 5. Работа регистра сдвига с сумматором по модулю 2 ; а – функциональная схема ;

- 4. Если сумматор отсутствует, то получается обычный регистр сдвига и при первом переключении сигнал 1 из ячейки

- 5. Совместная работа регистра и сумматора по модулю 2

- 6. В такте I I I сигнал 1 из ячейки X1 переписывается в ячейку X2 и через

- 7. Деление многочленов с помощью регистра и сумматоров Регистр с сумматорами по модулю 2 может быть использован

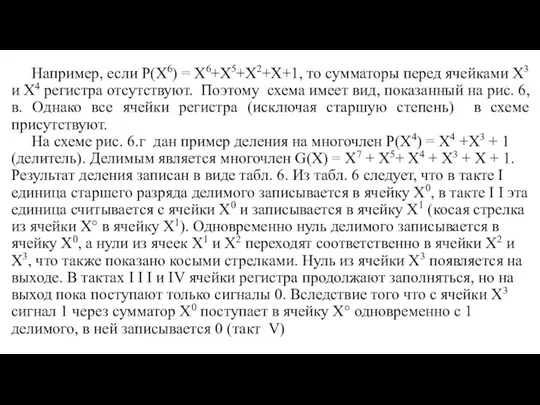

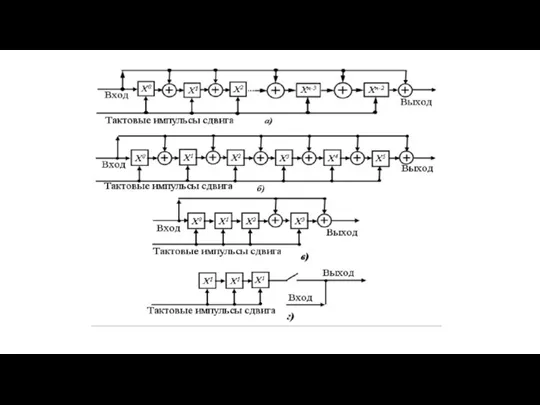

- 8. Например, если Р(Х6) = Х6+Х5+Х2+X+1, то сумматоры перед ячейками X3 и X4 регистра отсутствуют. Поэтому схема

- 9. Схемы деления многочлена на многочлен

- 10. Схемы деления многочлена на многочлен. а – многочлен n – степени, б – многочлен X6+X5+X4+X3+X2+X+1, в

- 11. Деление многочленов

- 12. Умножение многочленов Умножение многочленов с помощью регистра и сумматоров. Для умножения на заранее фиксированный многочлен (34)

- 14. Рис. 7. Схемы для умножения многочлена на многочлен и одночлен: а – многочлена n-степени, б –

- 15. Умножение многочленов.

- 16. Сравнивая схемы умножителей и делителей, можно сделать следующие выводы: 1) число ячеек регистра равно старшей степени

- 18. Скачать презентацию

Слайд 2ния

Рис. 4. Логический элемент сложения по модулю 2;

а — функциональная схема;

ния

Рис. 4. Логический элемент сложения по модулю 2;

а — функциональная схема;

в - таблица функционирования

Слайд 3

Рис. 5. Работа регистра сдвига с сумматором по модулю 2 ;

а –

Рис. 5. Работа регистра сдвига с сумматором по модулю 2 ;

а –

Слайд 4Если сумматор отсутствует, то получается обычный регистр сдвига и при первом переключении

Если сумматор отсутствует, то получается обычный регистр сдвига и при первом переключении

Таким образом, при отсутствии сумматора по модулю 2 число состояний регистра N = n, где n — число ячеек регистра.

В каждом такте (от I до VII, исключая нулевой) показано состояние ячеек регистра после записи и считывания информации. В исходном состоянии во всех ячейках регистра записан сигнал 0. В такте I ячейку Х° регистра записывается сигнал 1. Далее вторым тактовым импульсом происходит переписывание сигнала 1 из ячейки Х° в ячейку X1 (косая стрелка из ячейки Х° в ячейку X1). Работа схемы представлена в табл. 5.

Слайд 5Совместная работа регистра

и сумматора по модулю 2

Совместная работа регистра

и сумматора по модулю 2

Слайд 6 В такте I I I сигнал 1 из ячейки X1 переписывается в

В такте I I I сигнал 1 из ячейки X1 переписывается в

Сигналы 1 с ячеек Х° и X1 переписываются в ячейки X1 и X2 соответственно (такт VI), а в такте VII 1 заполнит только ячейку X2. В дальнейшем состояние ячеек регистра начнет повторяться, начиная с такта I.

Таким образом, применение сумматора позволяет увеличить число состояний схемы с трех до семи, а в общем случае до

N =2n – 1, так как нулевая комбинация никогда далее не повторяется.

Слайд 7Деление многочленов с помощью регистра и сумматоров

Регистр с сумматорами по модулю 2

Деление многочленов с помощью регистра и сумматоров

Регистр с сумматорами по модулю 2

Для деления любого многочлена на заранее фиксированный многочлен

где ai = 1 или 0, может быть использована схема рис. 6. а., в которой перед каждой ячейкой регистра имеется сумматор по модулю 2. Ячейка регистра для члена со старшей степенью и соответствующий ей сумматор отсутствуют. Это следует из процесса деления многочлена на многочлен, из которого вытекает, что старшие члены делимого и делителя, в которых всегда стоят единицы, складываясь по модулю 2, дают нуль. Для случая

схема делителя представлена на рис. 6, б.Ниже приведена схема для деления на многочлен, если в нем некоторая ai =0.

Слайд 8 Например, если Р(Х6) = Х6+Х5+Х2+X+1, то сумматоры перед ячейками X3 и X4

Например, если Р(Х6) = Х6+Х5+Х2+X+1, то сумматоры перед ячейками X3 и X4

На схеме рис. 6.г дан пример деления на многочлен Р(X4) = X4 +X3 + 1 (делитель). Делимым является многочлен G(X) = X7 + X5+ X4 + X3 + X + 1. Результат деления записан в виде табл. 6. Из табл. 6 следует, что в такте I единица старшего разряда делимого записывается в ячейку X0, в такте I I эта единица считывается с ячейки X0 и записывается в ячейку X1 (косая стрелка из ячейки Х° в ячейку X1). Одновременно нуль делимого записывается в ячейку X0, а нули из ячеек X1 и X2 переходят соответственно в ячейки X2 и X3, что также показано косыми стрелками. Нуль из ячейки X3 появляется на выходе. В тактах I I I и IV ячейки регистра продолжают заполняться, но на выход пока поступают только сигналы 0. Вследствие того что с ячейки X3 сигнал 1 через сумматор X0 поступает в ячейку Х° одновременно с 1 делимого, в ней записывается 0 (такт V)

Слайд 9Схемы деления многочлена на многочлен

Схемы деления многочлена на многочлен

Слайд 10Схемы деления многочлена на многочлен.

а – многочлен n – степени, б –

Схемы деления многочлена на многочлен.

а – многочлен n – степени, б –

в – многочлен X6+X5+X2+X+1, г – многочлен X4+X3+1

В том же такте на выходе появляется I и через сумматор X3 происходит запись 1 в ячейку X3 (обратная связь с ячейки X3 на ячейку Х° регистра и на ту же ячейку X3 показана косыми стрелками влево и вниз). В такте VI, хотя на вход поступает 0 делимого по обратной связи с ячейки X3, в ячейку X0 записывается 1. Однако из-за той же обратной связи в ячейке X3 происходит запись 0, так как сумматор X3 не пропустил два сигнала 1

Заполнение ячеек регистра в такте VII происходит без обратной связи, которая вновь сказывается в такте VIII. Частное читается сверху вниз.

Слайд 11Деление многочленов

Деление многочленов

Слайд 12Умножение многочленов

Умножение многочленов с помощью регистра и сумматоров. Для умножения на

Умножение многочленов

Умножение многочленов с помощью регистра и сумматоров. Для умножения на

В табл. 7 приведен процесс умножения многочлена X7+X5+X4+X3+X+1 на многочлен P(X)=X4+X3+1. В такте I единица старшего разряда записывается одновременно в ячейки X0, X3 и поступает на выход. В такте II на выход проходит сигнал 1 с ячейки X3, а с ячейки X0 он переходит в ячейку X1

В такте III сигнал 1 записывается в ячейки X0, X3 и проходит на выход, а сигнал I с ячейки X1 переходит в ячейку X2. В такте IV сигнал 1 записывается только в ячейку X0, но на выход он не проходит и не записывается в ячейку X3. Этому препятствуют сигналы 1 с ячеек X2 и X3.

Слайд 14 Рис. 7. Схемы для умножения многочлена на многочлен и одночлен:

а –

Рис. 7. Схемы для умножения многочлена на многочлен и одночлен:

а –

в- многочлена X4+X3+1, г- одночлена X3

Начиная с такта IX информация в регистр не поступает и регистр очищается, т. е. информация, записанная в такте VIII, такт за тактом подается на выход. Результат умножения (111011010011) читается сверху вниз.

Для умножения на одночлен Xn используют регистр без сумматора. Схема для умножения на одночлен X3 представлена на рис. 7, г). Пока на выход поступает множимое, ключ разомкнут и с регистра, в котором записаны нули, ничего не снимается. После поступления на выход последнего символа множимого ключ замыкается и в течение трех тактов с регистра считываются на выход три нуля, так как умножение на Xn эквивалентно приписыванию к множимому n нулей справа.

Слайд 15Умножение многочленов.

Умножение многочленов.

Слайд 16Сравнивая схемы умножителей и делителей, можно сделать следующие выводы:

1) число ячеек регистра

Сравнивая схемы умножителей и делителей, можно сделать следующие выводы:

1) число ячеек регистра

2) число сумматоров на единицу меньше числа ненулевых членов многочлена, на который производится деление или умножение, или на единицу меньше его веса;

3) при делении отбрасывается сумматор, соответствующий старшему члену многочлена, а при умножении - младшему. Например, при делении на многочлен

Р(Х)=Х4 + Х3 + 1 остаются сумматоры для Х3, Х°, а при умножении на этот же многочлен — сумматоры до ячейки Х3 и после нее;

Точные и приближенные методы

Точные и приближенные методы Развитие вычислительной техники

Развитие вычислительной техники Компьютеризация делопроизводства

Компьютеризация делопроизводства Тестовое задание. Мониторинг и анализ информационного пространства

Тестовое задание. Мониторинг и анализ информационного пространства Компьютерные технологии, типовое задание Mathcad IDM 2.0 company

Компьютерные технологии, типовое задание Mathcad IDM 2.0 company Элементарные логические операции

Элементарные логические операции Проект Пианино. Модуль 6. Учебный проект 2

Проект Пианино. Модуль 6. Учебный проект 2 Информационные модели на графах. 7 класс

Информационные модели на графах. 7 класс ERM (Entity-Relation Model) Анализ и проектирование структур данных с использованием CASEсредств

ERM (Entity-Relation Model) Анализ и проектирование структур данных с использованием CASEсредств Марафон “5 дней - 5 навыков”. Востребованные навыки в удаленной профессии

Марафон “5 дней - 5 навыков”. Востребованные навыки в удаленной профессии Сортировка вставками

Сортировка вставками Поле Чудес

Поле Чудес Лекция 1

Лекция 1 Школьная стенгазета как элемент истории повседневности

Школьная стенгазета как элемент истории повседневности Методики определения актуальных угроз безопасности информации

Методики определения актуальных угроз безопасности информации Особенности использования функциональных возможностей MS Power Point при создании презентации

Особенности использования функциональных возможностей MS Power Point при создании презентации Кибербезопасность в сети интернет для детей

Кибербезопасность в сети интернет для детей Информационные системы судопроизводства

Информационные системы судопроизводства Объект. Задания к уроку

Объект. Задания к уроку Операторы, реализирующие циклические алгоритмы

Операторы, реализирующие циклические алгоритмы Презентация на тему Геоинформационные системы(ГИС)

Презентация на тему Геоинформационные системы(ГИС)  Моделі системи глобальної інформаційної безпеки. Існуючі моделі

Моделі системи глобальної інформаційної безпеки. Існуючі моделі Презентация на тему Представление числовой информации в компьютере (10 класс)

Презентация на тему Представление числовой информации в компьютере (10 класс)  Разновидности поисковых систем

Разновидности поисковых систем Изучаем C#

Изучаем C# 05 указатели

05 указатели Алгоритм и его свойства

Алгоритм и его свойства Всемирная паутина (WWW)

Всемирная паутина (WWW)